International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

IARJSET

Vol. 3, Issue 8, August 2016

# Design of Parallel Adder/Subtractor using a Novel Reversible Logic Gate

A. Bhagyashree<sup>1</sup>, Babu Gundlapally<sup>2</sup>, T. Sammaiah<sup>3</sup>

M.Tech in VLSI System Design, Vaagdevi College of Engineering, Warangal, Telangana, India<sup>1</sup>

Associate Professor, Department of ECE, Vaagdevi College of Engineering, Warangal, Telangana, India<sup>2,3</sup>

Abstract: Reversibility plays an important role when energy efficient computations are considered Parity preserving property can be used for this. Reversible logic is a new emerging technology with many promising applications in optical information processing, low power (Complementary Metal Oxide Semiconductor) CMOS design, (De Oxy Ribonucleic Acid) DNA computing, etc. In industrial automation, comparators play an important role in segregating faulty patterns from good ones. In previous works, these comparators have been implemented with more number of reversible gates and computational complexity. All these comparators use propagation technique to compare the data. This will reduce the efficiency of the comparators. To overcome the problem a new 5\*5 parity preserving reversible gate is proposed in this paper, named as P2RG. The most significant aspect of this work is that it can work both as a full adder and a full subtractor by using one P2RG and Fredkin gate only. According to the control logic input the proposed design can works as an adder or a subtractor.

Keywords: (De Oxy Ribonucleic Acid) DNA, (Complementary Metal Oxide Semiconductor) CMOS design, P2RG.

# **I. INTRODUCTION**

Reversible circuits are composed of reversible gates. In fault tolerant reversible circuit is much more difficult than this circuits there is no information loss. Reversible a conventional logic circuit (Parhami, 2006). In this paper, circuits can produce unique output from each input and we propose a fault detection method based on parity vice versa, hence, there is a one-to-one correspondence preserving reversible logic gate. between input and output vectors (Thapliyal and Srinivas, 2006). So a reversible logic gate has an equal number of Present irreversible technologies dissipate a lot of heat in inputs and outputs (k ×k) (Babu and Chowdhury, 2005).

In ideal conditions, a reversible circuit has zero internal power dissipation because, it does not lose information. Under R. Landauer's research in the early 1960s, the amount of energy dissipated for every irreversible bit operation is given by KTLn2 joules, where K = 1.3806505 $\times$  10!23 J/K is the Boltzmann's constant and T is the between inputs and outputs which reduces the major absolute temperature at which operation is performed. But in 1973, Bennett showed that KTLn2 joules of energy can be saved from a system as long as the system permits the A Reversible logic is characterized by: regeneration of the inputs from produced outputs 1. Equal number of inputs and outputs. (Haghparast et al., 2009; Haghparast and Navi, 2008a; Thapliyal and Gupta, 2006).

A reversible gate with n-inputs and n-outputs is called a n  $\times$  n reversible gate (Sastry et al., 2006). In a n  $\times$  n reversible function, there are 2n input rows and 2n output operation since it has an equal number of inputs and rows in its truth table. In fact the output rows are a outputs with their unique one to one mapping. Some permutation of the input rows in the truth table (Kerntopf, reversible gates have already been proposed in literature 2002; Hung et al., 2006). Direct fan-outs from the like the controlled-not (CNOT) (proposed by Feynman) reversible gate and feedbacks from a gate output directly [3], Toffoli and Fredkin gates [4], IG Gate[5] and MIG to its inputs are not allowed (Sastry et al., 2006). Classical gate [6]. Reversible gates have various application in the logic gates are called irreversible since they cannot designing of adders, subtractors, multipliers[7], [8] etc, uniquely reconstruct the input vector states from the same like classical computers. The main focus of this output vector states. Synthesis and designing of a paper is to design a circuit that can work as adder as well reversible gate is different from traditional logic gates as subtratctor simultaneously with minimum numbers of (Haghparast and Sheikh, 2011). Therefore, constructing a

terms of bit loss which reduces life of the circuit. All logical operations in today's classical computers are irreversible.

It means extraction of input from the respective output is not possible. On the other hand, reversible computation has a salient feature of unique one to one mapping problem of power dissipation with no information loss.

- 2. There exists one to one mapping between the respective inputs and outputs.

- 3. Loops and fan out are not allowed.

In classical computers, only NOT gate performs reversible garbage outputs, constant inputs and area.

International Advanced Research Journal in Science, Engineering and Technology

# ISO 3297:2007 Certified

Vol. 3, Issue 8, August 2016

# **II. DESIGN CONSTRAINTS AND DEFINITIONS**

Minimizing the number of Ancillary (constant) Inputs: An extra, auxiliary bit or fixed qubit state that is added to the primary inputs in order to achieve the specific functionality but they need to be minimized for where, Iv and Ov are input and output vectors minimizing auxiliary storage.

#### Minimizing the number of Garbage Outputs:

Outputs that are not used further, needed only to make the function reversible (which results to minimize area and power).

Minimizing the Gate Count: Number of gates that are used to realize the system is gate count [9].

Fault Tolerance: Any physical device while performing classical or quantum computation is subjected to error either due to noise in the environment or fault in the device. It can be detected by fault tolerant computing. Although reversibility is able to recover bit loss, but it is unable to detect bit errors in the circuit [10]. Recent digital circuit designing is now focusing on the fault tolerant reversible circuits.

**Parity Preservation:** It can be used for the fault tolerance computation. Faults in the circuit can be detected by comparing the parity of inputs and outputs. The idea of the parity preserving property in the design reversible logic circuits was given by Parhami [11].

It is known that reversible gates have an equal number of inputs and outputs.

$A \bigoplus B \bigoplus C \bigoplus D = P \bigoplus Q \bigoplus R \bigoplus S$

Where A, B, C and D are gate inputs and P, Q, R and S are gate outputs.

#### **III. LITERATURE SURVEY**

#### **Reversible logic gates:**

**NOT gate:** NOT gate is a  $1 \times 1$  gate represented as shown in Fig.1. Since it is a  $1 \times 1$  gate, its quantum cost is zero (Thapliyal and Ranganathan, 2009; Rangaraju et al., 2010).

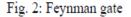

**Feynman Gate (FG):** Among the existing 2×2 reversible gates, Feynman gate which is shown in Fig. 2 is the most important gate. It can be represented as Iv = (A, B) Ov = (P)= A, Q = A $\oplus$ B), where, Iv and Ov are input and output vectors. Since it is a  $2 \times 2$  gate, it has a quantum cost of 1 Thapliyal and Ranganathan (2009) and Saiful (2010).

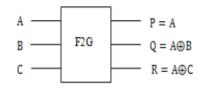

Feynman double Gate (F2G): Feynman double gate as a  $3 \times 3$  reversible gate is shown in Fig. 3. It can be showed as: Iv = (A, B, C),  $Ov = (P = A, Q = A \oplus B, R = A \oplus C)$ where, Iv and Ov are input and output vectors respectively.

F2G gate is a Feynman gate with one more input and one more output which the control input 'A' defines a second controlled NOT operation (Haghparast and Navi, 2008b). It has the quantum cost of 2.

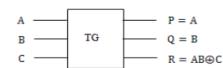

Toffoli Gate (TG): Toffoli gate is a 3×3 two-through reversible gate as shown in Fig. 4. It means that two of its outputs are same as the inputs. This gate can be represented as:

Iv = (A, B, C),  $Ov = (P = A, Q = B, R = AB \bigoplus C)$

respectively.

Toffoli gate is one of the most popular reversible gates and it has quantum cost of 5 (Thapliyal and Ranganathan, 2009; Chung and Wang, 2007).

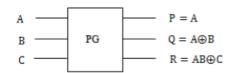

Peres Gate (PG): Peres gate also known as New Toffoli Gate (NTG) is a 3×3 reversible logic gate. It can be described as:

Iv = (A, B, C),  $Ov = (P = A, Q = A \oplus B, R = AB \oplus C)$ where, Iv and Ov are input and output vectors respectively.

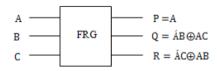

Fredkin Gate (FRG): Fig.6 shows 3\*3 Fredkin gate (FRG). It has A, B and input vector and output vector as P = A,Q= A'B  $\oplus$  AC and R = A'C  $\oplus$  AB.

If control input A = 0 then inputs B and C are showed clearly in outputs, else if A = '1' then inputs B and C are swapped and showed in outputs. It has quantum cost of 5 (Haghparast and Sheikh, 2011; Saiful, 2010).

New gate (NG): Another one of the interesting gate is New gate which is represented in Fig. 7. The advantage of the New gate is that, this gate can produce all the basic gates. It has the quantum cost of 7 (Hasan et al., 2003; Haghparast and Navi, 2007).

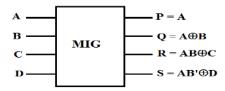

Modified IG Gate (MIG): Fig.8 shows 4\*4 Modified IG [11] gate. It has A, B, C and D input vector and output vector as P = A,  $Q = A \oplus B$ ,  $R = AB \oplus C$  and S = AB' $\oplus$  D.

Fig. 1: NOT gate

Fig. 3: Feynman double gate

Copyright to IARJSET

# IARJSET

#### International Advanced Research Journal in Science, Engineering and Technology ISO 3297:2007 Certified

Vol. 3, Issue 8, August 2016

Fig. 4: Toffoli gate

Fig. 5: Peres gate

Fig. 6: Fredkin gate

|   |        | 1 |                           |

|---|--------|---|---------------------------|

| А | <br>   |   | $\mathbf{P} = \mathbf{A}$ |

| В | <br>NG |   | $Q=AB\oplusC$             |

| С |        |   | R = ÁĆ⊕É                  |

Fig. 7: New gate

Fig.8 Modified IG Gate (MIG)

#### **IV. PROPOSED DESIGN**

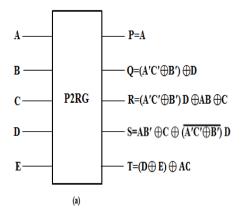

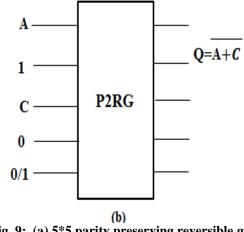

A new 5\*5 parity preserving reversible gate, P2RG is introduced in Fig.9 (a).

• This gate is one through which means one of its inputs is also an output.

• It is shown in Fig.9 (b) that Proposed gate is universal since it is able to perform NOR operation.

Fig. 9: (a) 5\*5 parity preserving reversible gate (P2RG) (b) P2RG as universal gate

When input B=1 and D=0 then output Q performs NOR operation i.e. (A+C)'. As it is known that NAND and NOR gates are universal gates so it can be concluded that it can be exploited to realize any arbitrary Boolean function.

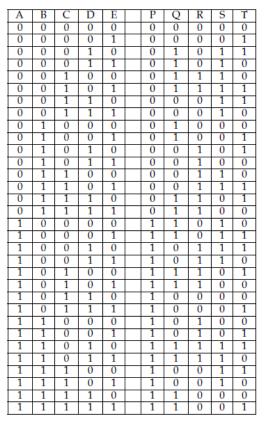

Truth table of this gate is shown in Table 1, where A, B, C, D and E are the inputs and P, Q, R, S and T are the outputs. It can be seen from the table that all the input and output vectors are uniquely related. The parity preserving property is promptly verified from the table by comparing the parity of the input to the parity of the output.

TABLE I: Truth Table of P2RG Gate

# IARJSET

# International Advanced Research Journal in Science, Engineering and Technology

ISO 3297:2007 Certified

Vol. 3, Issue 8, August 2016

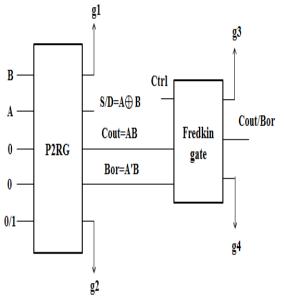

## A. Parity Preserving Half Adder/Subtract or

The parity preserving half adder/subtractor is Fig.10. Half adder and subtractor are the basic building in which g1, g2, g3 and g4 are garbage outputs. block to design full adder and subtractor. We need two input i.e. A and B to design a half adder/subtractor. No previous carry or borrow is needed in this. So, this design has two inputs A and B and a control line Ctrl which will control mode of operation, i.e. when Ctrl is at logic 0, the circuit will act as half adder and when ctrl is at logic 1, the circuit will act a s half subtractor. It will give three constant inputs and four garbage bits g1 to g4. Boolean expressions to realize the functionality of half adder and half subtractor are given below:

Sum/Difference =

$$A \bigoplus B$$

Carry =  $AB$

Borrow =  $A'B$

Fig. 10: Parity Preserving Half Adder/Subtractor using P2RG gate

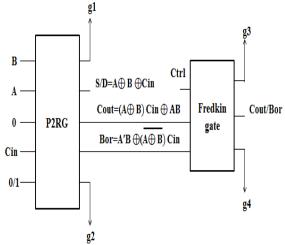

#### **B.** Parity Preserving Full Adder/Subtractor

Many adder designs using reversible gates by several authors have been studied. The proposed design will work as adder as well as subtractor on a single unit.

The parity preserving full adder/subtractor is realized using one P2RG gate and one Fredkin gate. In Fig.11, the circuit has three inputs A, B, Cin and a control line Ctrl which will control mode of operation. If Ctrl= 0, it will work as a full adder else it would function as a full subtractor. It has 2 constant inputs, C is set to 0 and E can be set to either 0 or 1. The basic Boolean expressions for sum/difference, carry and borrow are given below for full adder and subtractor:

$(Sum/Difference = (A \oplus B \oplus Cin))$

$(Carry = ((A \bigoplus B).Cin) \bigoplus AB))$

$(Borrow = ((A)'.B) \bigoplus (((A \bigoplus B)').Cin))$

Fig. 11: Parity Preserving Full Adder/Subtractor using P2RG gate

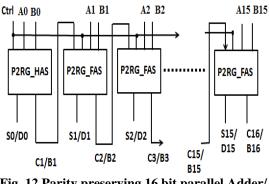

C. Parity Preserving 16 -bit Parallel Adder/Subtractor

Fig. 12 Parity preserving 16 bit parallel Adder/ Subtractor using P2RG gate

An n-bit parallel adder/subtractor will need a chain of (n-1) full adders/subtractor and one half adder/subtractor. Therefore 16-bit parity preserving parallel adder/subtractor is designed by using one parity preserving half adder/subtractor (P2RG HAS) and fifteen parity preserving full adder/subtractor (P2RG FAS). It has two 16-bit numbers which are A0 to A15 and B0 to B15 as inputs and a control line ctrl which will control the mode of operation. When ctrl line is set at logic 0, the circuit will perform 16-bit addition operation and when ctrl line is set at logic 1, the circuit will perform 16-bit subtraction.

The Carry/Borrow received after addition/ subtraction is represented by C1/B1 to C15/B15.Output carry/borrow of each block, i.e. C1/B1 to C15/B15 will be the third input for the next block. The outputs, Sum/Difference and Carry/Borrow are shown in the Fig.12 as S0/D0 to S15/D15 respectively. Fig.12 shows the parity preserving 16-bit parallel adder/subtractor.

# IARJSET

International Advanced Research Journal in Science, Engineering and Technology

ISO 3297:2007 Certified

# Vol. 3, Issue 8, August 2016

## V. RESULTS

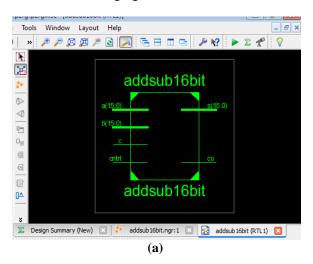

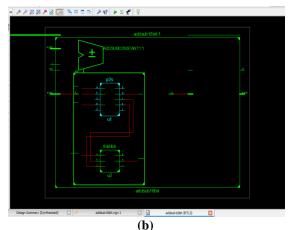

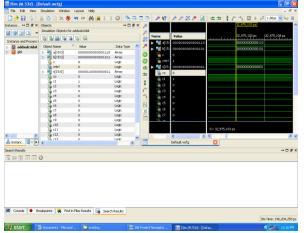

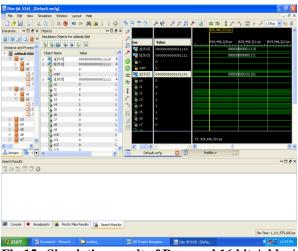

The entire architecture is modeled using Verilog. The coding is done on Xilinx ISE12.1 (xc6slx41-1ltqg144) at speed grade of -1. RTL Schematic view, Simulation and Timing report of 16 Bit Parallel Adder/Subtractor are shown in the following figures

Fig: 13 (a), (b) RTL Schematic of Proposed 16 bit parallel adder/subtractor

Fig 14. Simulation Result of Proposed 16 bit Adder/ Subtractor when ctrl=1(it acts as a Parallel Subtractor)

Fig 15. Simulation result of Proposed 16 bit Adder/ Subtractor when ctrl=0 (it acts as Parallel Adder)

| Design Overview                   |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------|---------|-------------------------|--|--|--|--|

| - Summary                         | Asynchronous Control Signals Information:                                                                         |                                                      |        |         |                         |  |  |  |  |

| - 108 Properties                  |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| - Module Level Utilization        | No asynchronous co                                                                                                | No asynchronous control signals found in this design |        |         |                         |  |  |  |  |

| - Timing Constraints              |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| - Pinout Report                   | Timing Summary:                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| - Clock Report                    |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| Static Timing                     | Speed Grade: -1                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| Errors and Warnings               | 1 A A                                                                                                             |                                                      |        |         |                         |  |  |  |  |

| Parser Messages                   | Minimum period:                                                                                                   | No park for                                          | her    |         |                         |  |  |  |  |

| Synthesis Messages                | Minimum input arrival time before clock: No path found                                                            |                                                      |        |         |                         |  |  |  |  |

| - Translation Messages            | Himmum import arrival time defore clock: No path found<br>Haximum output required time after clock: No path found |                                                      |        |         |                         |  |  |  |  |

| - 🗋 Map Messages                  | Maximum combinational path delay: 6.005ns                                                                         |                                                      |        |         |                         |  |  |  |  |

| Place and Route Messages          | DEALESSE CONDING                                                                                                  | croner been                                          | ueray. | 0.00303 |                         |  |  |  |  |

| - Timing Messages                 |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| - 🗋 Bitgen Messages               | Timing Details:                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| All Implementation Messages       |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| Detailed Reports                  | All values displayed in nanoseconds (ns)                                                                          |                                                      |        |         |                         |  |  |  |  |

| - 🖻 Synthesis Report              |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| Translation Report                |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| - 🗋 Map Report                    |                                                                                                                   | Timing constraint: Default path analysis             |        |         |                         |  |  |  |  |

| - D Place and Route Report        | Total number of                                                                                                   | Total number of paths / destination ports: 397 / 17  |        |         |                         |  |  |  |  |

| - D Post-PAR Static Timing Report |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| - D Power Report                  | Delay:                                                                                                            | Delay: 6.005ns (Levels of Logic = 11)                |        |         |                         |  |  |  |  |

| - D Bitgen Report                 | <ul> <li>Source:</li> </ul>                                                                                       | b<1> (PA)                                            | D)     |         |                         |  |  |  |  |

| thesis Report                     | Destination:                                                                                                      | CO (PAD)                                             |        |         |                         |  |  |  |  |

| Top of Report                     | -                                                                                                                 |                                                      |        |         |                         |  |  |  |  |

| Synthesis Options Summary         | Data Path: b<1>                                                                                                   | to co                                                |        |         |                         |  |  |  |  |

| HDL Parsing                       |                                                                                                                   |                                                      | Gate   | Net     |                         |  |  |  |  |

| HDL Elaboration                   | E Cell:in->out                                                                                                    | fanout                                               | Delay  | Delay   | Logical Name (Net Name) |  |  |  |  |

| HDL Synthesis                     |                                                                                                                   |                                                      |        |         |                         |  |  |  |  |

| HDL Synthesis Report              | TRUF: T->0                                                                                                        | 2                                                    | 0.003  | 0.784   | b 1 IBUF (b 1 IBUF)     |  |  |  |  |

| Advanced HDL Synthesis            | LUT6:10->0                                                                                                        |                                                      |        |         | u2/u3/g1 (c2)           |  |  |  |  |

| Advanced HDL Synthesis Report     | LUT6:19->0                                                                                                        |                                                      |        |         | u4/u3/g1 (c4)           |  |  |  |  |

| Low Level Synthesis               | LUT6:14->0                                                                                                        |                                                      |        |         | u6/u3/g1 (c6)           |  |  |  |  |

| Partition Report                  | LUI6:14->0                                                                                                        |                                                      |        |         | u8/u3/g1 (C8)           |  |  |  |  |

| Design Summary                    |                                                                                                                   | 3                                                    | v-360  | v.335   | antantār (nol           |  |  |  |  |

|                                   | * 4                                                                                                               |                                                      |        |         |                         |  |  |  |  |

Fig 16. Timing report of Proposed 16 bit Parallel Adder/Subtractor

#### **VI. APPLICATIONS**

Reversible logic is one of the most vital issue at present time and it has different areas for its application, those are low power CMOS, quantum computing, nanotechnology, cryptography, optical computing, DNA computing, digital signal processing (DSP), quantum dot cellular automata, communication, computer graphics. It is not possible to realize quantum computing without implementation of reversible logic

#### **VII. CONCLUSION**

In this study, we proposed a novel Parity Preserving Reversible gate. We also designed Parity Preserving Half-Adder/Subtractor circuit and a Parity Preserving reversible full-Adder/Subtractor circuit using P2RG gate. The proposed design can work as single unit that can acts as adder as well as subtractor depending upon our requirement. The proposed design offers less hardware complexity, less gate count, less garbage bits and constant inputs.

International Advanced Research Journal in Science, Engineering and Technology

ISO 3297:2007 Certified

Vol. 3, Issue 8, August 2016

## VIII. FUTURE SCOPE

In this paper we have worked on the Reversible logic gates on combinational circuits in future we can extend these to implement sequential circuits also.

## REFERENCES

- R. Landauer, "Irreversibility and heat generation in the computing process," IBM journal of research and development, vol. 5, no. 3, pp. 183–191, 1961.

- [2] C. H. Bennett, "Logical reversibility of computation," IBM journal of Research and Development, vol. 17, no. 6, pp. 525–532, 1973.

- [3] R. P. Feynman, "Quantum mechanical computers," Foundations of physics, vol. 16, no. 6, pp. 507–531, 1986.

- [4] E. Fredkin and T. Toffoli, Conservative logic. Springer, 2002.

- [5] M. Islam, Z. Begum et al., "Reversible logic synthesis of fault tolerant carry skip bcd adder," arXiv preprint arXiv: 1008.3288, 2010.

- [6] P. NG and M. Anandaraju, "Design and synthesis of fault tolerant full adder/subtractor using reversible logic gates."

- [7] P. Garg and S. Saini, "A novel design of compact reversible sg gate and its applications," in Communications and Information Technologies (ISCIT), 2014 14th International Symposium on. IEEE, 2014, pp. 400–403.

- [8] S. Saini and S. B. Mandalika, "A new bus coding technique to minimize crosstalk in vlsi bus," in Electronics Computer Technology (ICECT), 2011 3rd International Conference on, vol. 1. IEEE, 2011, pp. 424–428.

- USYD, "State Reduction," http://www.ee.usyd.edu.au/tutorials/ digital tutorial/part3/st-red.htm, 2008, [Online; accessed 19-July-2008].

- [10] G. Paul, A. Chattopadhyay, and C. Chandak, "Designing parity preserving reversible circuits," arXiv preprint arXiv: 1308.0840, 2013.

- [11] B. Parhami, "Fault-tolerant reversible circuits," in Signals, Systems and Computers, 2006. ACSSC'06. Fortieth Asilomar Conference on. IEEE, 2006, pp. 1726–1729.

- [12] P. Kaur and B. S. Dhaliwal, "Design of fault tolerant full adder/subtarctor using reversible gates," in Computer Communication and Informatics (ICCCI), 2012 International Conference on. IEEE, 2012,

#### BIOGRAPHIES

**A. Bhagyashree** is pursuing her M.Tech in VLSI SYSTEM DESIGN at Vaagdevi College of Engineering, Warangal, Telangana, India.

**Babu Gundlapally** is working as Associate Professor in Department of ECE at Vaagdevi College of Engineering, Warangal, Telangana, India.

**T. Sammaiah** is working as Associate Professor in Department of ECE at Vaagdevi College of Engineering, Warangal, Telangana, India.